CZ

EN

Popis

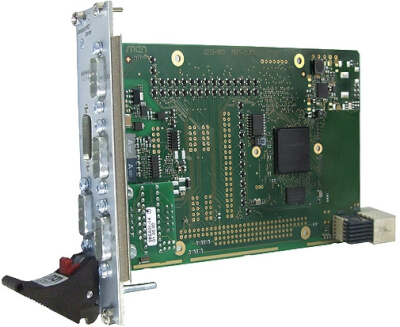

The G215 is a universal interface board based on 3U CompactPCI® Serial. The physical layer can be realized individually for each channel by means of SA-Adapters™.

SA-Adapters™ are small universal boards providing the line drivers for legacy serial I/O, fieldbus interfaces and other small I/O functions. Most SA-Adapters™ use 9-pin D-Sub connectors which are accessible at the front panel. Alternatively, the adapter can be connected to the front panel via ribbon cable. The SA concept allows to add additional I/O interfaces to the G215, enhancing flexibility with regard to the line transceivers and isolation requirements.

Two SA-Adapters™ can be mounted directly on the G215, the other maximum six adapters need more front-panel space and are connected to the carrier via ribbon cable. The G215 comes in a standard configuration with five pre-defined functions on 8 HP: two CAN interfaces, two UARTs and one 8-channel binary I/O interface. SA-Adapters™ are not included in the delivery, because different types are available, e.g. for the UARTs. They can be ordered as needed.

The board's I/O functions are realized by means of an FPGA, making it a very flexible, inexpensive solution for dedicated serial I/O. The card can become "everything" from a customized I/O combination to a specialized 8-port CAN card or even an intelligent I/O board including a Nios® soft core, on 4, 8 or 12 HP. As an option, the I/O signals can also be accessed via rear I/O on CompactPCI® Serial connectors P3 and P4. The FPGA is loaded automatically after power-up from a 4 MB serial Flash. It is also possible to access this Flash to update its contents.

Up to 64 MB DDR2 SDRAM (32 MB addressable by MEN IP core) is available for complementing the functions of the FPGA. This DRAM can be used for example as a large buffer memory for more complex protocols.

Fotogalerie

NAVRHNEME VÁM ŘEŠENÍ NA KLÍČ

Hledáte technologického partnera? Neváhejte se na nás obrátit.