CZ

EN

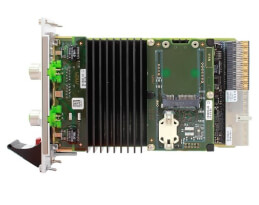

Základní informace

Main Features

- 2x Intel Atom E6xx, 512 MB DDR2 RAM (each) for onboard dual redundancy

- 1x Intel Atom E6xx, 1 GB DDR2 for I/O

- Independent supervisors for each block

- Fail-safe and fail-silent board architecture

- Clustering of two F75P to raise availability

- Event logging

- Certifiable up to SIL 4 (with report from TÜV SÜD)

- SIL 4 certification packages available for hardware and software (QNX)

- Developed according to EN 50129, EN 50128 and IEC 61508

- Full EN 50155 compliance

- -40 to +85C qualified

- Conformal coating

Specifikace

Technical Data

Blokové schéma

Fotogalerie

Ke stažení

NAVRHNEME VÁM ŘEŠENÍ NA KLÍČ

Hledáte technologického partnera? Neváhejte se na nás obrátit.