CZ

EN

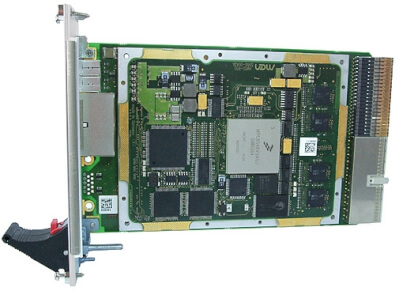

Základní informace

Main Features

- 32-bit CompactPCI and PICMG 2.30 PlusIO

- 8 HP or 12 HP with front I/O

- MPC8548 (or MPC8543), up to 1.5 GHz

- Up to 2 GB (ECC) DDR2 SDRAM

- Up to 128 KB FRAM, 2 MB SRAM

- Up to 16 GB SSD Flash

- Standard front I/O: 2 Gb Ethernet, 2 USB

- Standard rear I/O: 4 USB, 2 SATA

- FPGA for user-defined I/O functions (option)

- MENMON BIOS for PowerPC cards

- -40 to +70C (8 HP) (screene

Specifikace

Volitelné

Blokové schéma

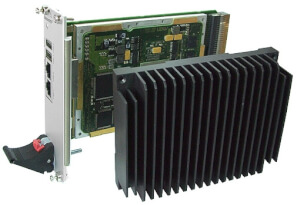

Fotogalerie

Ke stažení

NAVRHNEME VÁM ŘEŠENÍ NA KLÍČ

Hledáte technologického partnera? Neváhejte se na nás obrátit.